## Data Sheet, V1.5, May 2005

www.DataSheet4U.com

# HYE18P128160AF-9.6 HYE18P128160AF-12.5 HYE18P128160AF-15

Synchronous Burst CellularRAM<sup>™</sup> (1.5G) CellularRAM

**Memory Products**

Edition 2005-5

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

#### **Attention please!**

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# HYE18P128160AF-9.6 HYE18P128160AF-12.5 HYE18P128160AF-15

Synchronous Burst CellularRAM<sup>™</sup> (1.5G) CellularRAM

**Memory Products**

## HYE18P128160AF-9.6, HYE18P128160AF-12.5, HYE18P128160AF-15

| Revision Hist      | ory: 2005-5                                                                                                                                       | V1.5<br>www.DataSheet4U.co |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Previous Version:  | 1.4 (Target data sheet)                                                                                                                           |                            |

| Page               | Subjects (major changes since last revision)                                                                                                      |                            |

| 23                 | DPD Duration time adjusted                                                                                                                        |                            |

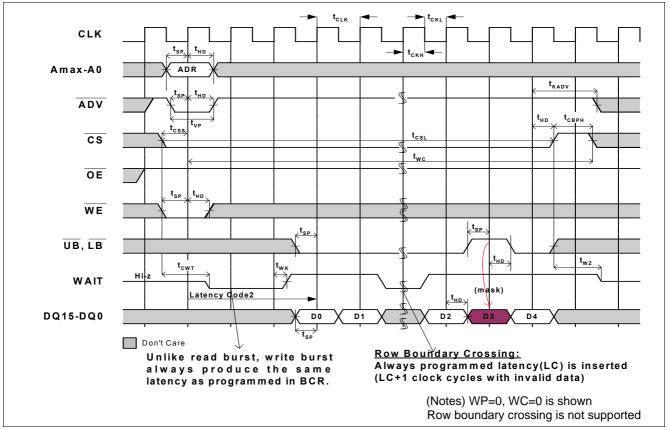

| <b>30</b> , 31     | Row boundary crossing is not supported in all cases                                                                                               |                            |

| 19, 37, 41         | CRE timing clarified in asynchronous control register access                                                                                      |                            |

| Previous Version:  | 1.3 (Target data sheet)                                                                                                                           |                            |

| All                | Min. Duration of DPD mode is set to 1ms                                                                                                           |                            |

| 14, 19, 20, 37, 45 | $\overline{\text{UB}}$ , $\overline{\text{LB}}$ low required for register read (FCR)                                                              |                            |

| 19, 20, 45         | Clarified WAIT behavior in synchronous register access                                                                                            |                            |

| 18                 | BCR.bit6 has no effect.                                                                                                                           |                            |

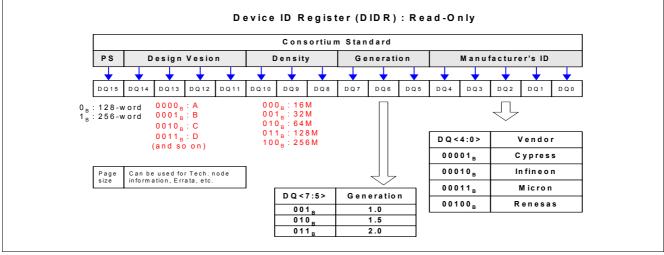

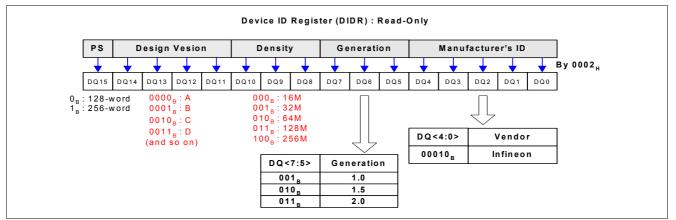

| 34                 | DIDR.bit15 reads out the information of page size. If no use, please ignore the bit.                                                              |                            |

| 56                 | Adjusted the values of Operating Currents                                                                                                         |                            |

| Previous Version:  | 1.2 (Target data sheet)                                                                                                                           |                            |

| Page               | Subjects (major changes since last revision)                                                                                                      |                            |

| All                | Adjusted CLK frequency target Vs. latency code in fixed latency mode                                                                              |                            |

| Previous Version:  | 1.1 (Target data sheet)                                                                                                                           |                            |

| All                | $V_{\rm DD}$ , min = 1.7V (contact factory for the part of 1.65V min)                                                                             |                            |

| All                | Wireless operating temperature goes down to - 30°C                                                                                                |                            |

| All                | Variable lat=2 reaches 66MHz max for 12.5 part                                                                                                    |                            |

| 10, 11             | J5 and J6 ball : "NC" to "RFU"                                                                                                                    |                            |

| 33, 56             | Density and Design Version fields are added to DIDR.                                                                                              |                            |

| Asynchronous       | Value change in $t_{OHZ}$ , $t_{WP}$ , $t_{DS}$ , $t_{AX}$ removed from the spec. (per spec alignment)                                            |                            |

| Synchronous        | Value change in t <sub>CWT</sub> , t <sub>CSS</sub> , t <sub>CKH/L</sub> , t <sub>SP</sub> , t <sub>T</sub> , t <sub>KOH</sub> per spec alignment |                            |

| Synchronous        | $t_{\text{KADV}}$ is added to specify timing requirement between last data-in to new burst_init.                                                  |                            |

| Previous Version   | n: 1.0 (Target data sheet)                                                                                                                        |                            |

| All                | All the spec features compatible to HYE18P64160AC V1.1 spec.                                                                                      |                            |

## We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: techdoc.mp@infineon.com

| <b>1</b><br>1.1 | Overview                                                          |    |

|-----------------|-------------------------------------------------------------------|----|

| 1.2             | General Description                                               |    |

| 1.3             | HYE18P128160AF-9.6/12.5/15 Ball Configuration                     |    |

| 1.4             | HYE18P128160AF-9.6/12.5/15 Ball Definition and Description        |    |

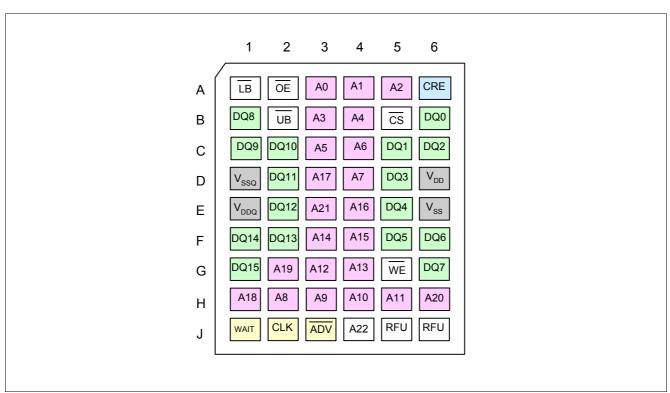

| 1.5             | Functional Block Diagram                                          |    |

| 1.6             | Commands                                                          |    |

| 1.6.1           | Asynchronous Commands                                             |    |

| 1.6.2           | Synchronous Commands                                              |    |

|                 |                                                                   |    |

| 2               | Functional Description                                            |    |

| 2.1             | Power-Up and Initialization                                       |    |

| 2.2             | Access To The Control Register Map                                |    |

| 2.3             | Refresh Control Register                                          |    |

| 2.3.1           | Partial Array Self Refresh (PASR)                                 |    |

| 2.3.2           | Deep Power Down Mode                                              |    |

| 2.3.3           | Temperature Compensated Self Refresh (TCSR)                       |    |

| 2.3.4           | Power Saving Potential in Standby When Applying PASR, TCSR or DPD |    |

| 2.3.5           | Page Mode Enable/Disable                                          |    |

| 2.4             | Bus Control Register                                              |    |

| 2.4.1           | Latency Mode / Code                                               |    |

| 2.4.1.1         | Variable latency mode                                             |    |

| 2.4.1.2         | Fixed latency mode                                                |    |

| 2.4.1.3         | Burst Write always produces fixed latency                         |    |

| 2.4.1.4         | Burst Interrupt operation                                         |    |

| 2.4.1.5         | End-of-Row Condition                                              |    |

| 2.4.2           | Read Burst Configurations/Sequences                               |    |

| 2.4.3           | WAIT Signal in Synchronous Burst Mode                             |    |

| 2.4.4           | Output Impedance                                                  |    |

| 2.5             | Self-Refresh                                                      |    |

| 2.6             | Device ID Register (DIDR)                                         |    |

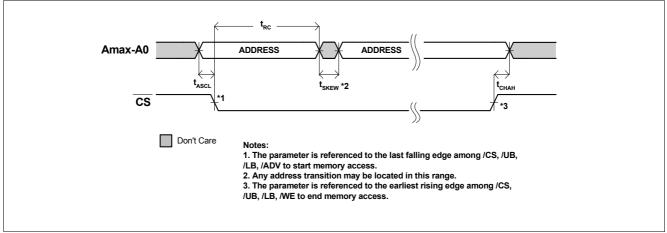

| 2.7             | Consideration on Address Skew                                     |    |

| 2.8             | SRAM-Type Mode                                                    |    |

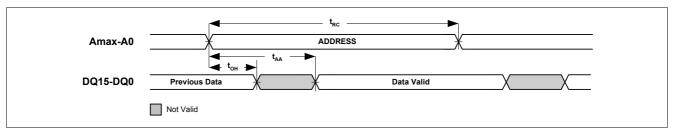

| 2.8.1           | Asynchronous Read                                                 |    |

| 2.8.2           | Page Mode                                                         |    |

| 2.8.3           | Asynchronous Write                                                |    |

| 2.9             | NOR-Flash-Type Mode                                               |    |

| 2.9.1           | -,                                                                | 43 |

| 2.9.2           |                                                                   | 44 |

| 2.9.3           |                                                                   | 45 |

| 2.9.4           |                                                                   | 47 |

| 2.10            |                                                                   | 50 |

| 2.10.1          | ,                                                                 | 50 |

| 2.10.2          |                                                                   | 50 |

| 2.11            | General AC Input/Output Reference Waveform                        | 54 |

| 3               | Electrical Characteristics                                        | 55 |

| 3.1             |                                                                   | 55 |

| 3.2             |                                                                   | 55 |

| 3.3             |                                                                   | 56 |

| 3.4             |                                                                   | 56 |

|                 | Package Outlines                                                  |    |

| 4               |                                                                   |    |

| 5               | Appendix : S/W Register Entry Mode ("4-cycle method")             | 58 |

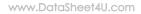

| Figure 1   | CellularRAM - Interface Configuration Options.                                                                                                                                  | 10 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

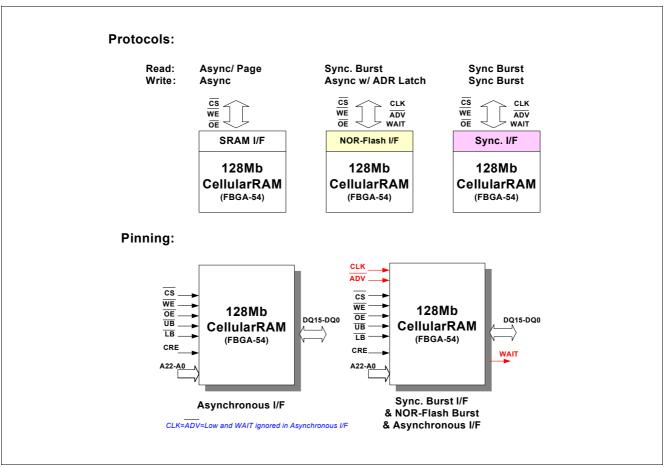

| Figure 2   | Standard Ballout - HYE18P128160AF-9.6/12.5/15                                                                                                                                   | 11 |

| Figure 3   | Functional Block Diagram.                                                                                                                                                       |    |

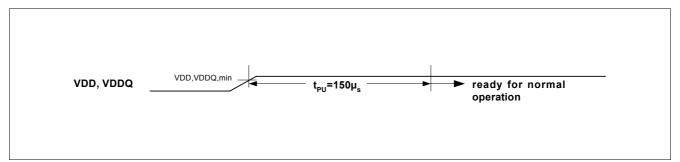

| Figure 4   | Power Up Sequence                                                                                                                                                               |    |

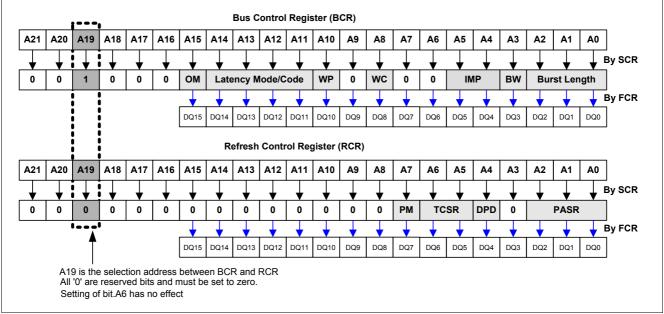

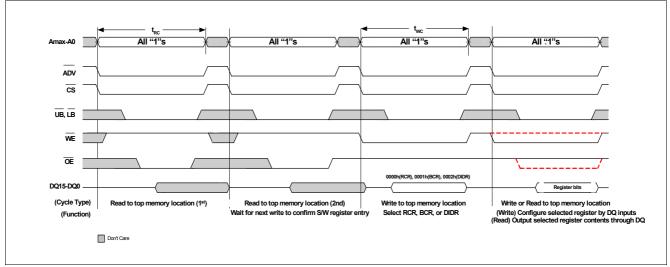

| Figure 5   | The two Control Registers (Write and Read access)                                                                                                                               |    |

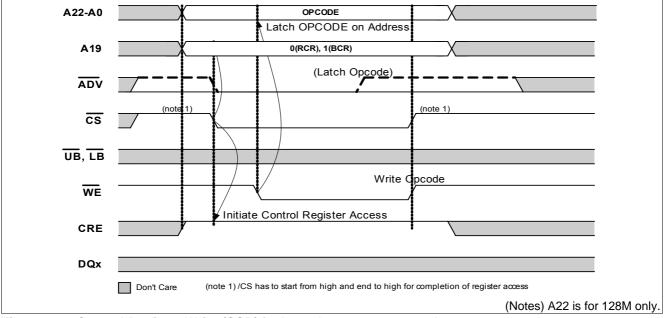

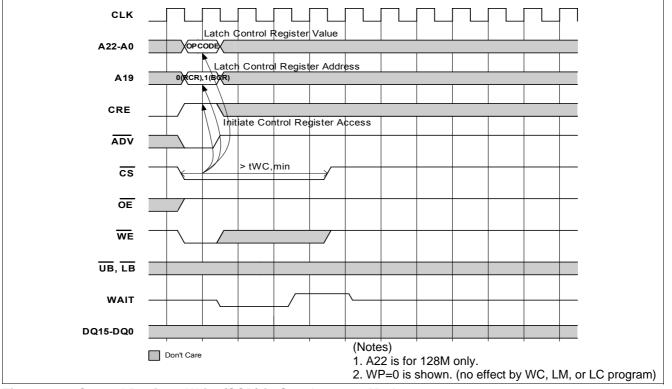

| Figure 6   | Control Register Write (SCR) in Asynchronous command                                                                                                                            |    |

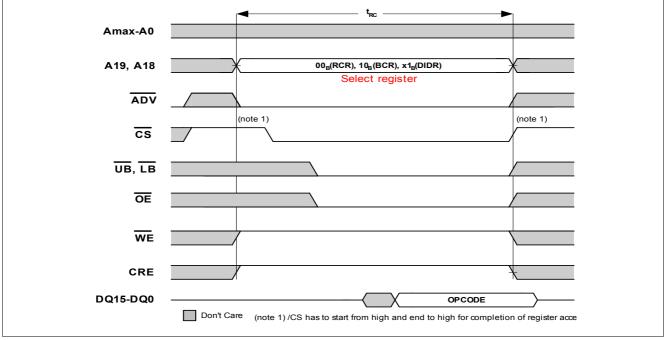

| Figure 7   | Control Register Read (FCR) in Asynchronous command.                                                                                                                            |    |

| Figure 8   | Control Register Write (SCR) in Synchronous Mode                                                                                                                                |    |

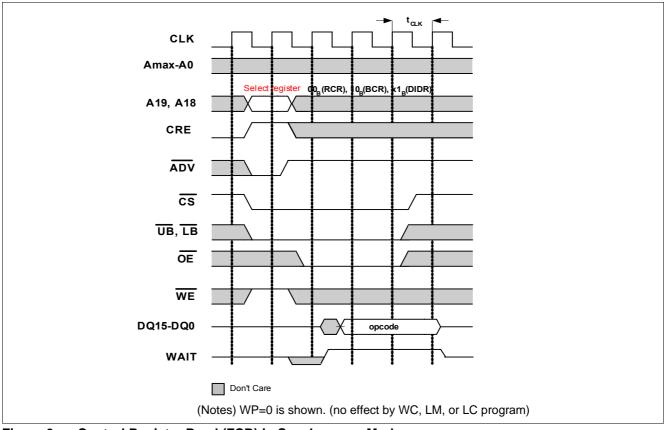

| Figure 9   | Control Register Read (FCR) in Synchronous Mode                                                                                                                                 |    |

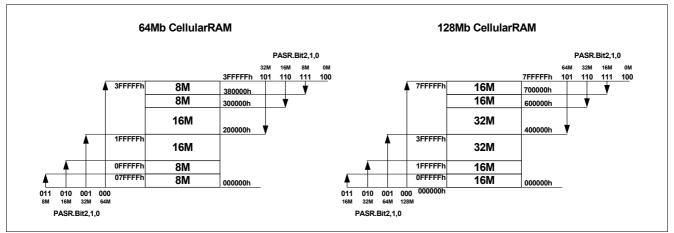

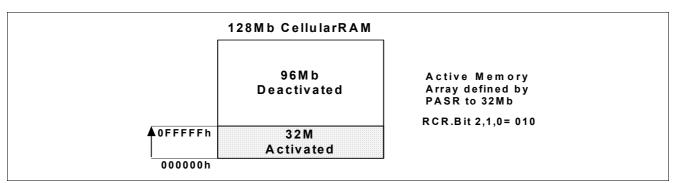

| Figure 10  | PASR Programming Scheme                                                                                                                                                         |    |

| Figure 11  | PASR Configuration Example.                                                                                                                                                     |    |

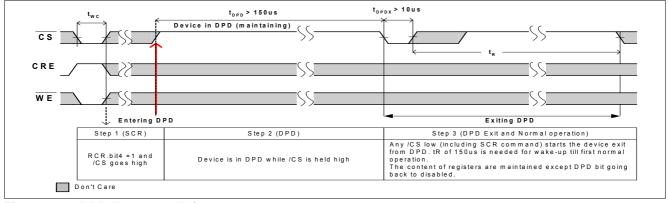

| Figure 12  | DPD Entry and Exit.                                                                                                                                                             |    |

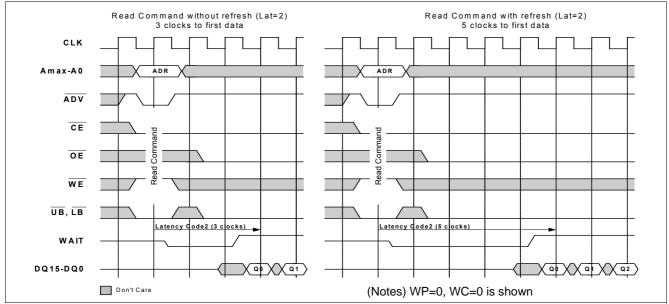

| Figure 13  | Variable Latency Mode - Functional Diagram (Lat=2, Variable, WC=0 shown)                                                                                                        |    |

| -          |                                                                                                                                                                                 |    |

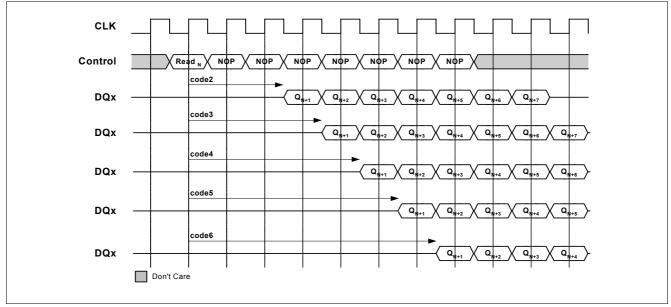

| Figure 14  | Latency Code - Functional Diagram                                                                                                                                               |    |

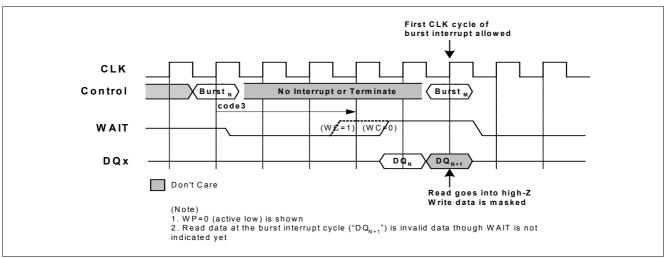

| Figure 15  | Burst Interrupt after Burst_init command                                                                                                                                        |    |

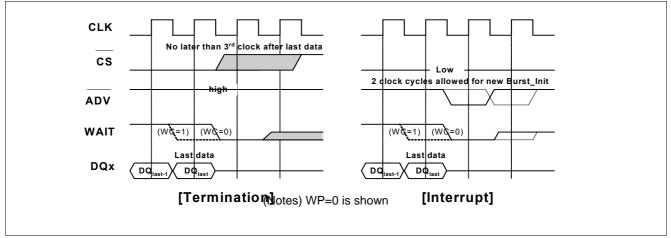

| Figure 16  | WAIT Timing and Recommended Operation at the End of Row                                                                                                                         |    |

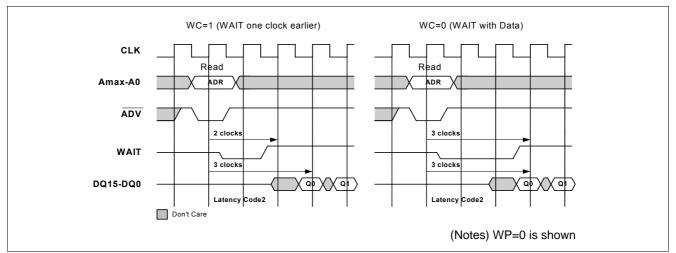

| Figure 17  | WAIT Function by configuration (WC) - Lat=2, WP=0                                                                                                                               |    |

| Figure 18  | Device ID Register (DIDR) Mapping.                                                                                                                                              |    |

| Figure 19  | Timing Diagram of Address Skew                                                                                                                                                  | 35 |

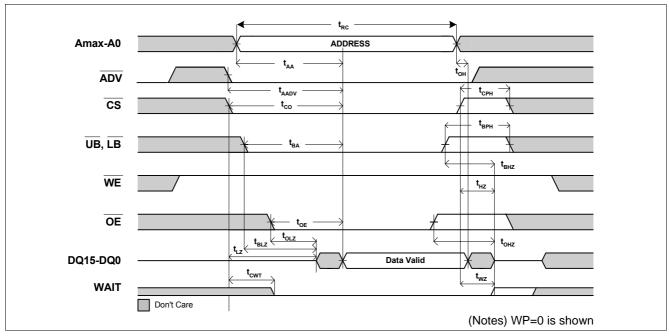

| Figure 20  | Asynchronous Read - Address Controlled ( $\overline{CS} = \overline{OE} = V_{IL}$ , $\overline{WE} = V_{IH}$ , $\overline{UB}$ and/or $\overline{LB} = V_{IL}$ , $CRE = V_{IL}$ |    |

|            |                                                                                                                                                                                 | 36 |

| Figure 21  | Asynchronous Read ( $\overline{WE} = V_{H}$ , CRE = $V_{L}$ )                                                                                                                   |    |

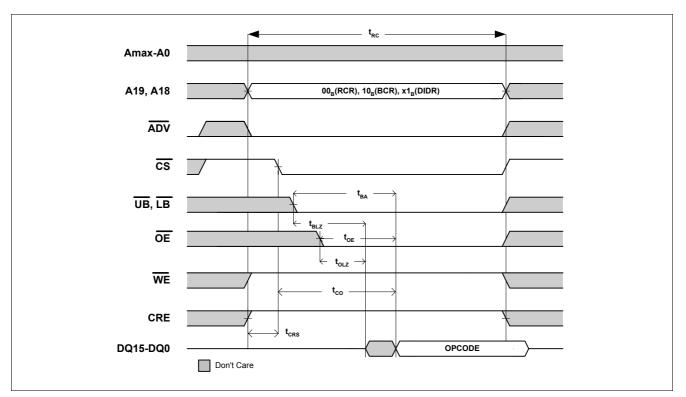

| Figure 22  | Asynchronous Control Register Read                                                                                                                                              |    |

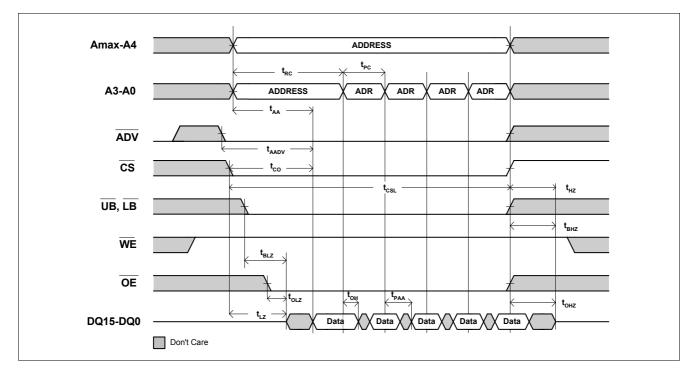

| Figure 23  | Asynchronous Page Read Mode (CRE = $V_{IL}$ , ADV = $V_{IL}$ )                                                                                                                  |    |

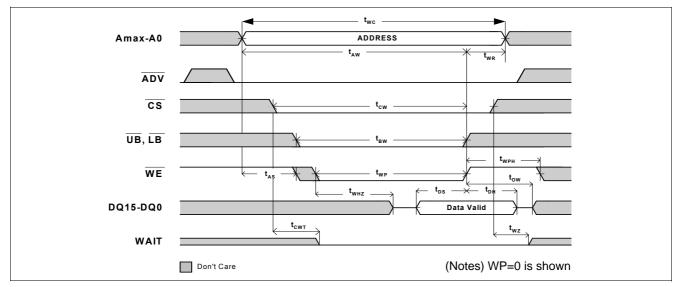

| Figure 24  | Asynchronous Write - $\overline{WE}$ Controlled ( $\overline{OE} = V_{IH}$ or $V_{IL}$ , CRE = $V_{IL}$ )                                                                       |    |

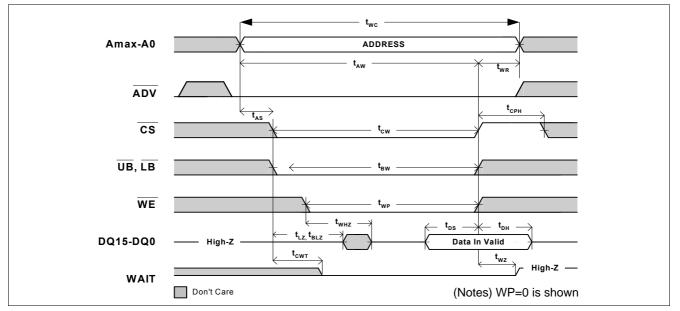

| Figure 25  | Asynchronous Write - $\overline{CS}$ Controlled ( $\overline{OE} = V_{IH}$ or $V_{IL}$ , CRE = $V_{IL}$ )                                                                       |    |

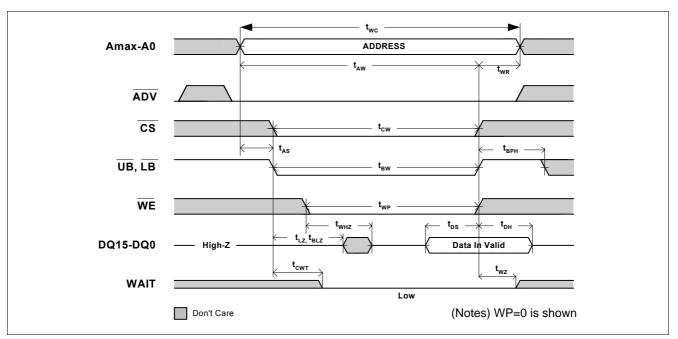

| Figure 26  | Asynchronous Write - $\overline{UB}$ , $\overline{LB}$ Controlled ( $\overline{OE} = V_{IH}$ or $V_{IL}$ , $CRE = V_{IL}$ )                                                     |    |

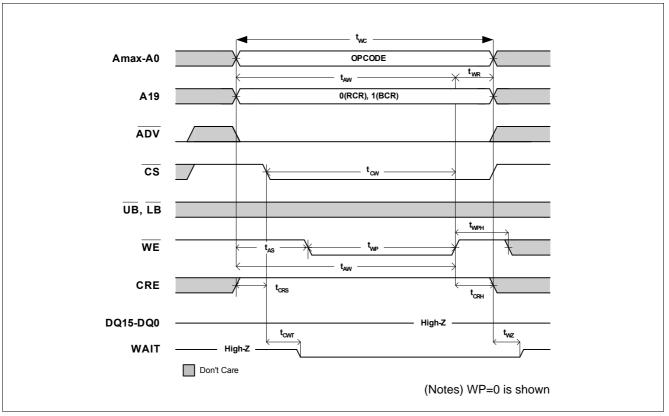

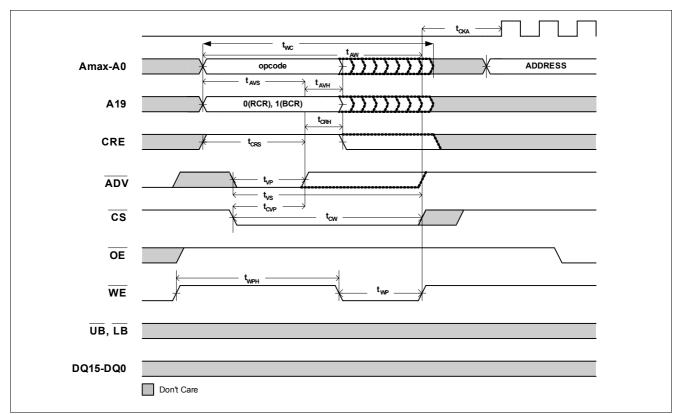

| Figure 27  | Asynchronous Write to Control Register ( $\overline{OE} = V_{IH}$ or $V_{IL}$ )                                                                                                 | 41 |

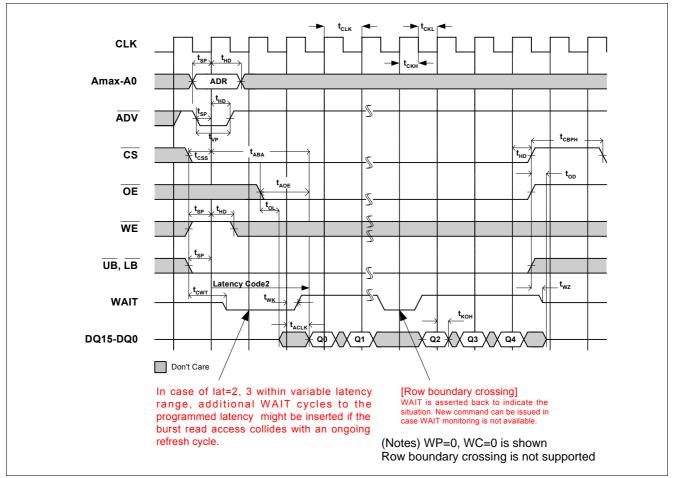

| Figure 28  | Synchronous Read Burst (CRE = $V_{IL}$ )                                                                                                                                        | 43 |

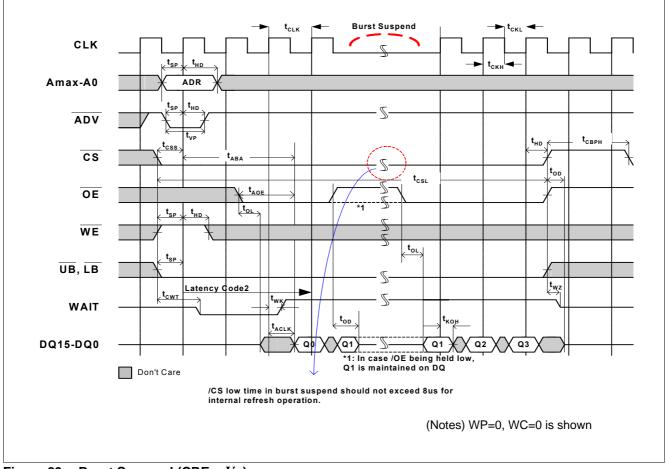

| Figure 29  | Burst Suspend (CRE = $V_{IL}$ ).                                                                                                                                                | 44 |

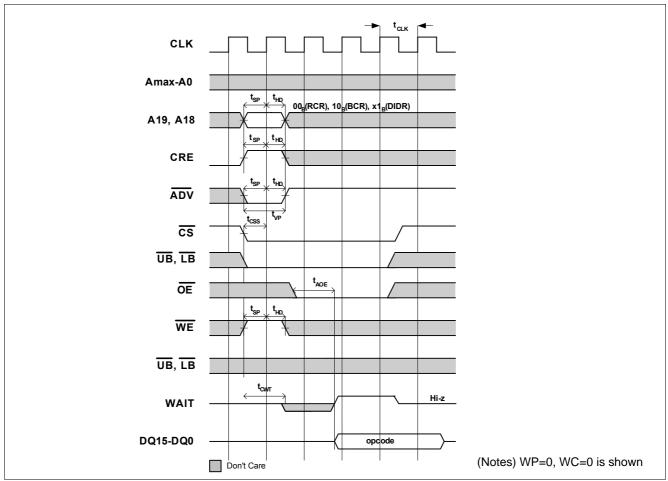

| Figure 30  | Synchronous Control Register Read                                                                                                                                               | 45 |

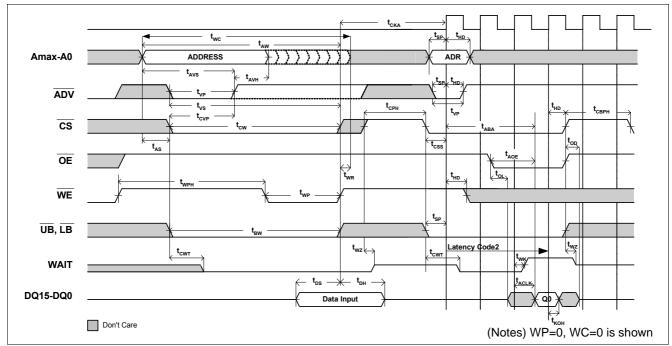

| Figure 31  | Asynchronous Write with Address Latch (ADV) Control (followed by single-burst read)                                                                                             | 47 |

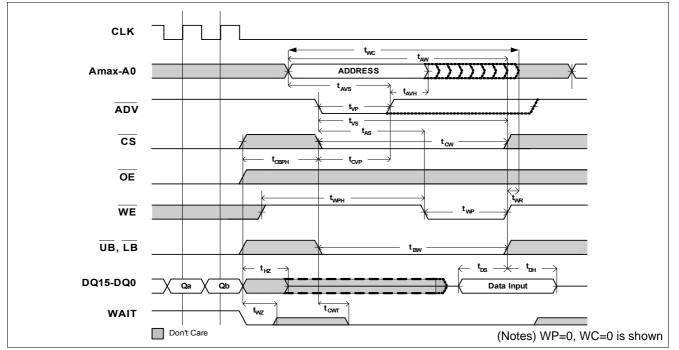

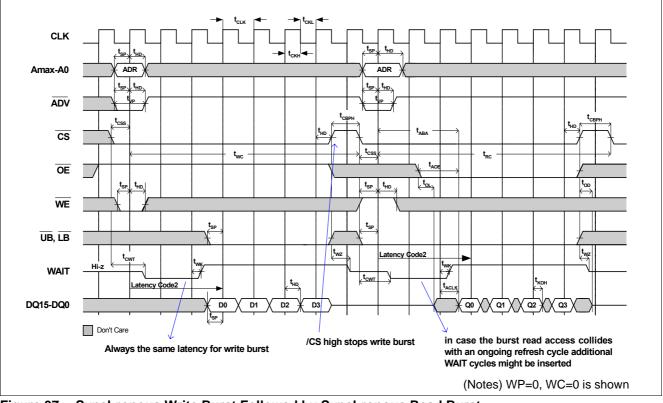

| Figure 32  | Asynchronous Write with Address Latch (ADV) Control.                                                                                                                            |    |

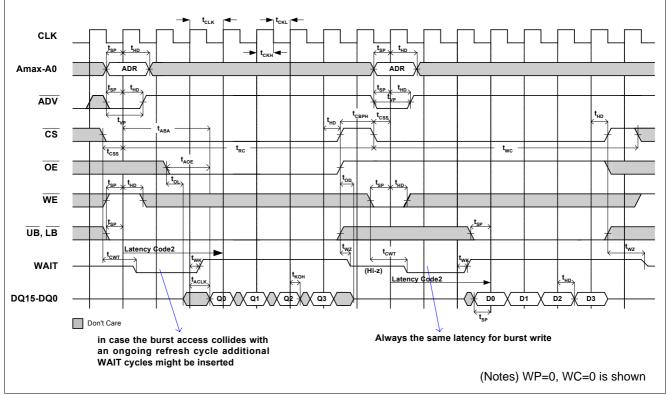

| Figure 33  | Asynchronous Write To Control Register in NOR-Flash Mode.                                                                                                                       | 48 |

| Figure 34  | Synchronous Write Burst (CRE = $V_{\parallel}$ )                                                                                                                                |    |

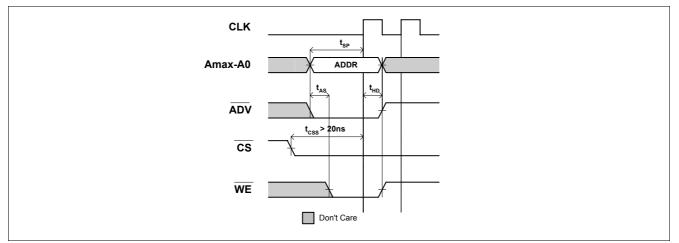

| Figure 35  | Synchronous Write command with extended t <sub>CSS</sub>                                                                                                                        |    |

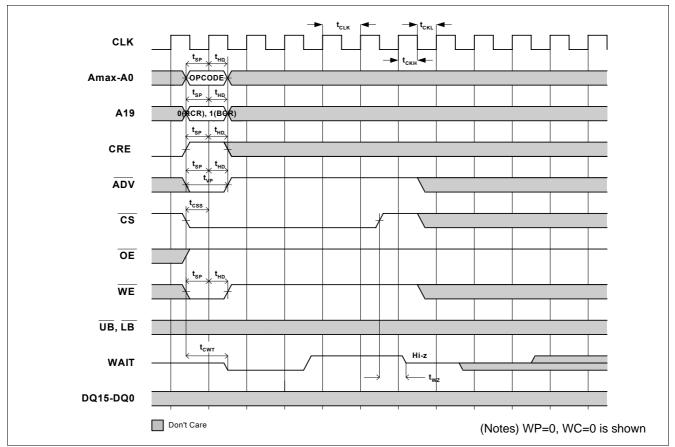

| Figure 36  | Synchronous Write to Control Register                                                                                                                                           |    |

| Figure 37  | Synchronous Write Burst Followed by Synchronous Read Burst.                                                                                                                     |    |

| Figure 38  | Synchronous Read Burst Followed by Synchronous Write Burst.                                                                                                                     |    |

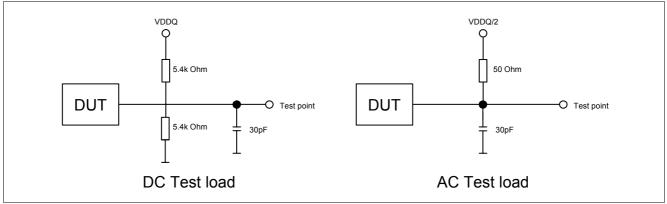

| Figure 39  | DC / AC Output Test Circuit                                                                                                                                                     |    |

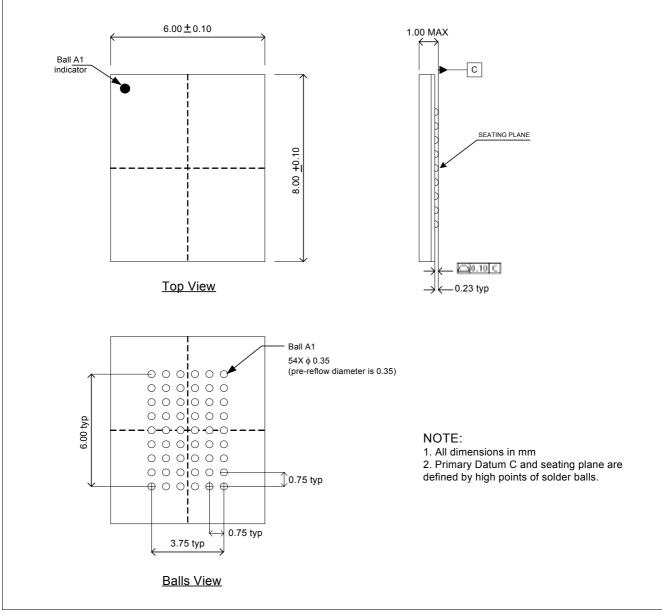

| Figure 40  | PG-VFBGA-54 (Plastic Very Thin Fine Pitch Ball Grid Array Package - Green Package)                                                                                              |    |

| Figure 41  |                                                                                                                                                                                 | 58 |

| Figure 42  | RCR Mapping in S/W Register Entry                                                                                                                                               |    |

| Figure 43  | BCR Mapping in S/W Register Entry                                                                                                                                               |    |

| Figure 44  | DIDR Mapping in S/W Register Read.                                                                                                                                              |    |

| i iguic ++ |                                                                                                                                                                                 | 00 |

| Table 1<br>Table 2 | Product Selection & Marking                             |    |

|--------------------|---------------------------------------------------------|----|

| Table 3            | Asynchronous Command Table                              |    |

| Table 4            | •                                                       | 14 |

| Table 5            | Synchronous Command Table                               | 15 |

| Table 6            | Description of Synchronous Commands                     |    |

| Table 7            | Timing Parameters for DPD Operation                     |    |

| Table 8            | Standby Currents When Applying PASR, TCSR or DPD        |    |

| Table 9            | Latency Mode / Code Configuration                       |    |

| Table 10           | Burst Sequences                                         |    |

| Table 11           | Output Impedance                                        | 33 |

| Table 12           | Timing Parameters - Address Skew                        | 35 |

| Table 13           | Timing Parameters - Asynchronous Read.                  | 39 |

| Table 14           | Timing Parameters - Asynchronous Write                  | 42 |

| Table 15           | Timing Parameters - Synchronous Read Burst              | 46 |

| Table 16           | Timing Parameters - Asynchronous Write With ADV Control | 49 |

| Table 17           | Timing Parameters - Synchronous Read/Write Burst        | 54 |

| Table 18           | Absolute Maximum Ratings                                | 55 |

| Table 19           | Recommended DC Operating Conditions                     | 55 |

| Table 20           | DC Characteristics                                      | 55 |

| Table 22           | Pin Capacitances                                        | 56 |

| Table 21           | Operating Characteristics                               | 56 |

## 128M Synchronous Burst CellularRAM<sup>™</sup> (1.5G) CellularRAM

## HYE18P128160AF-9.6 HYE18P128160AF-12.5 HYE18P128160AF-15

## 1 Overview

## 1.1 Features

- High density (1T1C-cell) Synchronous 128Mbit Pseudo-Static RAM

- Designed for cell phone applications low power, high density, refresh-free operation (CellularRAM)

- CellularRAM1.5G of more features, maintaining functional-compatibility to 1st-generation CellularRAM

- Organization 8M × 16

- High bandwidth:

- 104 MHz synchronous burst read/write, 20 ns page read (16-word), 70 ns random access

- 1.8 V single power supply ( $V_{DD}$  for core and  $V_{DDO}$  for I/O)

- Low power optimized design

- $I_{\text{ACTIVE}} = 25 \text{ mA} @70 \text{ ns}$  random cycle (with output disabled)

- $-I_{SB} = 250 \ \mu A$ , data retention mode

- $I_{\text{DPD}} = < 10 \ \mu\text{A}$  (typ), non-data retention mode

- Low power features

- Partial Array Self-Refresh (PASR)

- Deep Power Down Mode (DPD)

- Temparature Compensated Self-Refresh (TCSR) by the control of On-chip Temperature Sensor (OCTS)

- User configurable interface supporting three different access protocols (values from 9.6 part)

- asynchronous SRAM protocol, 70 ns random access cycle time, 20 ns page mode (read only) cycle time

- NOR-Flash burst protocol, 70 ns write cycle time, 104 MHz burst mode read cycle

- Full synchronous interface protocol, 70 ns random cycle time, 104 MHz burst mode read/write cycle

- User settings for NOR-Flash burst or in synchronous mode

- fixed burst length of 4/8/16/32 words or continuous burst mode

- latency mode (variable or fixed) and various latency codes at desired CLK frequency

- wrap mode function available for both read and write burst

- WAIT signal polarity and timing configurable

- Driver strength of full, 1/2, or 1/4

- Write burst operates at fixed latency regardless of latency mode

- 2 sets of programmable registers (RCR & BCR) accessed (set or fetch) by CRE-pin control or S/W entry mode

- 1 set of read-only register for device ID accessed via fetch register command

- Byte read/write control by UB/LB

- Wireless operating temperature range from -30 °C to +85 °C

- PG-VFBGA-54 chip-scale package Green Product (9 × 6 ball grid)

## Table 1 Product Selection & Marking

| HYE18P1           | 28160AF                          |           |                   | -9.6           |           | -12.5    |         | -15                    |  |  |  |

|-------------------|----------------------------------|-----------|-------------------|----------------|-----------|----------|---------|------------------------|--|--|--|

| Maximum I         | nput CLK frequency               | (MHz) La  | at = 2            | 66             |           | 66       |         | 40                     |  |  |  |

|                   |                                  | La        | at = 3            | 104            |           | 80       |         | 66                     |  |  |  |

| Min. Rando        | om Cycle time (t <sub>RC</sub> ) | 1         |                   | 70 ns          |           | 70 ns    |         | 85 ns                  |  |  |  |

| Ordering In       | formation                        |           |                   | contact factor | У         |          |         | contact factory        |  |  |  |

| HY                | E                                | <u>18</u> | P                 | 128            | <u>16</u> | <u>0</u> | Α       | E                      |  |  |  |

| Infineon          | Wireless                         | 1.8V      | CellularRAM       | 128M           | x16       | Synch    | Product | Green Package          |  |  |  |

| Memory<br>Product | temperature<br>range             | Supply    | Product<br>Family | 64: 64M        |           | Burst    | Version | W: KGD<br>(Wafer Form) |  |  |  |

Top-side view (ball down) J4 is NC for 64Mb and A22 for 128Mb

Overview

## 1.2 General Description

The Synchronous Burst CellularRAM<sup>™</sup> (1.5G) (CellularRAM) is designed to better serve the growing memory density and bandwidth demand in 2.5G and 3G cellular phone application. Its high density 1T1C-cell concept, the multi-protocol interface capabilities, its highly optimized low power design and its refresh-free operation make the CellularRAM the perfect fit for advanced baseband applications.

Configured in synchronous burst mode, a peak bandwidth of > 200 Mbyte/s is achieved at the max. clock rate of 104 MHz. The burst length can be programmed and set to either fixed burst lengths of 4, 8, 16- or 32-words<sup>1)</sup> or set to continuous mode. The 16-word burst mode is specially designed for cached processor designs to speed up cache re-fill operations. The addition of fixed latency mode to 1st-generation CellularRAM expands the support into legacy application where NOR-type burst flash has been adopted.

In NOR-Flash interface, burst read accesses are synchronous whereas write accesses are of asynchronous nature. This is to retain compatibility to today's NOR-Flash protocols and thus to make sure that existing baseband designs do get instantly a performance gain in read direction by deploying the NOR-Flash burst protocol. The different access protocols that are supported by the CellularRAM are illustrated in **Figure 1**. Data byte control ( $\overline{UB}$ ,  $\overline{LB}$ ) is featured in all modes and provides dedicated lower and upper byte access.

Figure 1 CellularRAM - Interface Configuration Options

The CellularRAM can be operated from a single 1.8 V power supply feeding the core and the output drivers. The chip is fabricated in Infineon Technologies advanced low power 0.11  $\mu$ m process technology and comes in a PG-VFBGA-54 package.

<sup>1) 1</sup> word is equal 16 bits

Overview

## 1.3 HYE18P128160AF-9.6/12.5/15 Ball Configuration

Figure 2 Standard Ballout - HYE18P128160AF-9.6/12.5/15

Note: Figure 2 shows top view

Overview

## 1.4 HYE18P128160AF-9.6/12.5/15 Ball Definition and Description

| Table 2                                                | Ball Desc         | ription - HYE18P128160AF-9.6/12.5/15                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball                                                   | Туре              | Detailed Function                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLK                                                    | Input             | <b>Clock Signal</b><br>In synchronous burst mode, address and command inputs and data are referenced to the<br>positive (rising) edge of CLK. In asynchronous SRAM-type mode and write accesses in<br>NOR-Flash operation mode, the CLK signal must be tied down to low.                                                                                                                                                                 |

| CRE                                                    | Input             | <b>Control Register Enable</b><br>CRE set to high enables the access to the control register map. By applying the Set<br>Control Register (SCR) command (see <b>Table 3</b> ) the address bus is loaded into the<br>selected control register, while Fetch Control Register (FCR) reads the contents of it onto<br>DQ pins.                                                                                                              |

| ADV                                                    | Input             | Address Valid<br>ADV signals in NOR-Flash and full synchronous mode that a valid address is present on<br>the address bus. In NOR-Flash read mode and full synchronous mode the address is<br>latched on the programmed clock edge while ADV is held low. In NOR-Flash write mode<br>ADV can be used to latch the address, but can be held low as well. In asynchronous<br>SRAM-type mode ADV needs to be active, it may be tied to low. |

| <u>CS</u>                                              | Input             | <b>Chip Select</b><br>CS enables the command decoder when low and disables it when high. When the<br>command decoder is disabled new commands are ignored, addresses are don't care and<br>outputs are forced to high-Z. Internal operations, however, continue. For the details,<br>please refer to the command tables in <b>Chapter 1.6</b> .                                                                                          |

| OE                                                     | Input             | Output Enable $\overline{OE}$ controls DQ output driver. $\overline{OE}$ low drives DQ, $\overline{OE}$ high sets DQ to high-Z.                                                                                                                                                                                                                                                                                                          |

| WE                                                     | Input             | Write Enable $\overline{WE}$ set to low while $\overline{CS}$ is low initiates a write command.                                                                                                                                                                                                                                                                                                                                          |

| UB, LB                                                 | Input             | Upper/Lower Byte Enable<br>UB enables the upper byte DQ15-8 (resp. LB DQ7 0) during read/write operations.<br>UB (LB) deassertion prevents the upper (lower) byte from being driven during read or<br>being written.                                                                                                                                                                                                                     |

| WAIT                                                   | Output<br>3-state | Wait State Signal<br>In synchronous mode, WAIT signal indicates the host system when the output data is<br>valid during read and when the input data should be asserted during write operation,<br>though monitoring of WAIT is not mandatory for write burst, since a write burst operates<br>at fixed latency always.<br>In asynchronous mode, the signal has to be ignored.                                                           |

| A <22:0>                                               | Input             | Address Inputs<br>During a Control Register Set operation by CRE access, the address inputs define the<br>register settings.                                                                                                                                                                                                                                                                                                             |

| DQ <15:0>                                              | I/O               | Data Input/Output The DQ signals $\overline{0}$ to $\overline{15}$ form the 16-bit data bus.                                                                                                                                                                                                                                                                                                                                             |

| $1 \times V_{\text{DD}}$<br>$1 \times V_{\text{SS}}$   | Power<br>Supply   | Power Supply, Core<br>Power and Ground for the internal logic.                                                                                                                                                                                                                                                                                                                                                                           |

| $1 \times V_{\text{DDQ}}$<br>$1 \times V_{\text{SSQ}}$ | Power<br>Supply   | <b>Power Supply, I/O Buffer</b><br>Isolated Power and Ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                  |

| 2 × RFU                                                | -                 | Reserved for Future Use (RFU)<br>Please do not connect. J5 and J6 are reserved for future use. See ballout in Figure 2 on<br>Page 11.                                                                                                                                                                                                                                                                                                    |

## 128M Synchronous Burst CellularRAM<sup>™</sup> (1.5G) CellularRAM

## HYE18P128160AF-9.6 HYE18P128160AF-12.5 HYE18P128160AF-15

## 1.5 Functional Block Diagram

## 1.6 Commands

The supported command set depends on the selected operation mode. By default the CellularRAM device is reset to the asynchronous SRAM-type mode after power-up. To put the device in a different operation mode the Bus Configuration Register (BCR) must be programmed first accordingly. The valid control input states and sequences are listed below in asynchronous commands (while CLK is held low) or synchronous commands. Other control signal combinations are not supported.

## 1.6.1 Asynchronous Commands

In the SRAM-type operation mode, all commands are of asynchronous nature. Write operation in NOR-Flash mode is done asynchronously as well. **Table 3** lists the asynchronous commands and CLK has to be held low for entire asynchronous mode operation.

| Operation Mode                  | Power Mode                   | CS | ADV | WE | ŌĒ              | UB/<br>LB       | CRE | A19         | A18         | Amax - A0          | DQ15:0                            |

|---------------------------------|------------------------------|----|-----|----|-----------------|-----------------|-----|-------------|-------------|--------------------|-----------------------------------|

| READ                            | Active                       | L  | L   | Н  | L               | L <sup>2)</sup> | L   | V           | V           | ADR                | DOUT                              |

| WRITE                           | Active                       | L  | L   | L  | X <sup>3)</sup> | L <sup>2)</sup> | L   | V           | V           | ADR                | DIN                               |

| Set Control<br>REGISTER (SCR)   | Active                       | L  | L   | L  | X <sup>3)</sup> | Х               | Н   | L<br>H      | L<br>L      | RCR DIN<br>BCR DIN | Х                                 |

| Fetch Control<br>REGISTER (FCR) | Active                       | L  | L   | Н  | L               | L               | Н   | L<br>H<br>X | L<br>L<br>H | Х                  | RCR bits<br>BCR bits<br>Device ID |

| NO OPERATION                    | Standby~Active <sup>4)</sup> | L  | Х   | Н  | Н               | Х               | L   | Х           | Х           | Х                  | High-Z                            |

| DESELECT                        | Standby                      | Н  | Х   | Х  | Х               | Х               | Х   | Х           | Х           | Х                  | High-Z                            |

| DPD <sup>5)</sup>               | DPD                          | Н  | Х   | Х  | Х               | Х               | Х   | Х           | Х           | Х                  | High-Z                            |

## Table 3 Asynchronous Command Table<sup>1)</sup>

1) CLK has to be held low for entire asynchronous operation. Amax is A22 for 128Mb.

- 3) During a write access invoked by WE set to low the OE signal is ignored.

- 4) Stand-by power mode applies only to the case when CS goes low from DESELECT while no address change occurs. Toggling address results in active power mode. Also, NO OPERATION from any active power mode by keeping CS low consumes the power higher than stand-by mode.

- 5) After entry, CS has to be held high to maintain DPD. CS low-going starts wake-up out of DPD and automatically reset DPD control bit (RCR Bit 4) to be diabled whether it is SCR command or not. All the other contents of control registers should be maintained during DPD in the same state when it was before this mode.

Note: 'L' represents a low voltage level, 'H' a high voltage level, 'X' represents "Don't Care", 'V' represents "Valid".

| Mode  | Description                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ  | The READ command is used to perform an asynchronous read cycle. The signals, UB and LB, define whether only the lower, the upper or the whole 16-bit word is output.                                                                                                                                                                                                    |

| WRITE | The WRITE command is used to perform an asynchronous write cycle. The data is latched on the rising edge of either $\overline{CS}$ , $\overline{WE}$ , $\overline{UB}$ , $\overline{LB}$ , whichever comes first. The signals, $\overline{UB}$ and $\overline{LB}$ , define whether only the lower, the upper or the whole 16-bit word is latched into the CellularRAM. |

## Table 4 Description of Asynchronous Commands

<sup>2)</sup> **Table 3** reflects the behaviour if UB and LB are asserted to low. If only either of the signals, UB or LB, is asserted to low only the corresponding data byte will be output or written (UB enables DQ15 - DQ8, LB enables DQ7 - DQ0).

| Mode                      | Description                                                                                                                                                                                                                                                                              |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SET CONTROL REGISTER      | The control registers are loaded via the address inputs A19, A15 - A0 performing<br>an asynchronous write access. Please refer to the control register description for<br>details. The SCR command can only be issued when the CellularRAM is in idle<br>state.                          |

| FETCH CONTROL<br>REGISTER | The content of selected control register is loaded via DQ15-DQ0 by performing this command. Please refer to the control register description for details. The FCR command can only be issued when the CellularRAM is in idle state.                                                      |

| NO OPERATION              | The NOP command is used to perform a no operation to the CellularRAM, which is selected ( $\overline{CS} = 0$ ). Operations already in progress are not affected. Power consumption of this command mode varies by address change and initiating condition.                              |

| DESELECT                  | The DESELECT function prevents new commands from being executed by the CellularRAM. The CellularRAM is effectively deselected. I/O signals are put to high impedance state.                                                                                                              |

| DPD                       | DPD stops all refresh-related activities and entire on-chip circuit operation.<br>Current consumption drops below 25 $\mu$ A. Wake-up from DPD also requires<br>150 $\mu$ s to get ready for normal operation. The use of DPD mode for duration of<br>no longer than 1ms is not allowed. |

## Table 4 Description of Asynchronous Commands (cont'd)

## 1.6.2 Synchronous Commands

In NOR-Flash-type mode read commands are performed in a synchronous burst, whereas both read and write in synchronous mode.

All synchronous commands are defined by the states of the control signals  $\overline{CS}$ ,  $\overline{ADV}$ , and  $\overline{WE}$  ( $\overline{UB}$ ,  $\overline{LB}$  and  $\overline{OE}$  controls output at read asynchronously and  $\overline{UB}$ ,  $\overline{LB}$  masks input data during write in synchronous way) at the positive (rising) edge of the clock signal, CLK. To enable the synchronous commands, the device has to be programmed in the Bus Configuration Register (BCR) first accordingly.

Table 5 lists the truth table for the supported synchronous commands.

| Operation Mode           | Power Mode                   | CLK  | CS | ADV | WE | UB/<br>LB       | CRE | A19         | A18         | Amax - A0          | DQ15:0                            |

|--------------------------|------------------------------|------|----|-----|----|-----------------|-----|-------------|-------------|--------------------|-----------------------------------|

| BURST INIT<br>READ       | Active                       | L->H | L  | L   | Н  | L               | L   | V           | V           | ADR                | Х                                 |

| BURST READ               | Active                       | L->H | L  | Н   | Х  | L <sup>2)</sup> | Х   | Х           | Х           | Х                  | DOUT <sup>3)</sup>                |

| BURST INIT<br>WRITE      | Active                       | L->H | L  | L   | L  | Х               | L   | V           | V           | ADR                | Х                                 |

| BURST WRITE              | Active                       | L->H | L  | Н   | Х  | L <sup>2)</sup> | Х   | Х           | Х           | Х                  | DIN                               |

| SET CONTROL<br>REGISTER  | Active                       | L->H | L  | L   | L  | Х               | Н   | L<br>H      | L<br>L      | RCR DIN<br>BCR DIN | Х                                 |

| FETCHCONTROL<br>REGISTER | Active                       | L->H | L  | L   | Н  | L               | Н   | L<br>H<br>X | L<br>L<br>H | Х                  | RCR bits<br>BCR bits<br>Device ID |

| NO OPERATION             | Standby~Active <sup>4)</sup> | L->H | L  | Н   | Н  | Х               | L   | Х           | Х           | Х                  | High-Z <sup>5)</sup>              |

| DESELECT                 | Standby                      | L->H | Н  | Х   | Х  | Х               | Х   | Х           | Х           | Х                  | High-Z                            |

| DPD <sup>6)</sup>        | DPD                          | L    | Н  | Х   | Х  | Х               | Х   | Х           | Х           | Х                  | High-Z                            |

Table 5Synchronous Command Table<sup>1)</sup>

1) Synchronous commands are sampled at rising edge of CLK except DPD. Amax is A22 for 128Mb.

- 2) **Table 5** reflects the behaviour if UB and LB are asserted to low. If only either of the signals, UB or LB, is asserted to low only the corresponding data byte will be output or written (UB enables DQ15 DQ8, LB enables DQ7 DQ0). If both signals are disabled the device is put in deselect mode.

- 3) Output driver controlled by the asynchronous OE control signal

- 4) Stand-by power mode applies only to the case when  $\overline{CS}$  goes low from DESELECT while no address change occurs. NO OPERATION from any active power mode by keeping  $\overline{CS}$  low consumes the power higher than stand-by mode.

- 5) The asynchronous OE control signal has to be asserted to 'H'.

- 6) After entry,  $\overline{CS}$  has to be held high to maintain DPD.  $\overline{CS}$  low-going starts wake-up out of DPD and automatically reset DPD control bit (RCR Bit 4) to be diabled whether it is SCR command or not. All the other contents of control registers should be maintained during DPD in the same state when it was before this mode.

Note: 'L' represents a low voltage level, 'H' a high voltage level, 'X' represents "Don't Care", 'V' represents "Valid".

| Mode                      | Description                                                                                                                                                                                                                                                                                 |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BURST INIT                | The BURST INIT command is used to initiate a synchronous burst access and to latch the burst start address. The burst length is determined by the setting in the Bus Configuration Register.                                                                                                |

| BURST READ                | The BURST READ command is used to perform a synchronous burst read access. The first data is output after the number of clock cycles as defined by the programmed latency mode.                                                                                                             |

| BURST WRITE               | The BURST WRITE command is used to perform a synchronous burst write access. The point of time when the first data is written is indicated by the WAIT signal. It varies with the selected clock frequency and the occurrence of a refresh cycle.                                           |

| SET CONTROL REGISTER      | The control registers are loaded via the address inputs A19, A15 - A0 performing a single word burst. Please refer to the control register description for details. The SCR command can only be issued when the CellularRAM is in idle state and no bursts are in progress.                 |

| FETCH CONTROL<br>REGISTER | The content of selected control register is loaded on DQ15 - DQ0 by performing this command like a single read burst. Please refer to the control register description for details. The FCR command can only be issued when the CellularRAM is in idle state and no bursts are in progress. |

| NO OPERATION              | The NOP command is used to perform a no operation to the CellularRAM, which is selected ( $\overline{CS} = 0$ ). Operations already in progress are not affected.                                                                                                                           |

| DESELECT                  | The DESELECT function prevents new commands from being executed by the CellularRAM. The CellularRAM is effectively deselected. I/O signals are put to high impedance state.                                                                                                                 |

| DPD                       | DPD stops all refresh-related activities and entire on-chip circuit operation.<br>Current consumption drops below 25 $\mu$ A. Wake-up from DPD also requires 150 $\mu$ s to get ready for normal operation. The use of DPD mode for duration of no longer than 1ms is not allowed.          |

Table 6

Description of Synchronous Commands

#### Functional Description

## 2 Functional Description

## 2.1 Power-Up and Initialization

The power-up and initialization sequence guarantees that the device is preconditioned to the user's specific needs. Like conventional DRAMs, the CellularRAM must be powered up and initialized in a predefined manner.  $V_{\text{DD}}$  and  $V_{\text{DDQ}}$  must be applied at the same time to the specified voltage while the input signals are held in "DESELECT" state ( $\overline{\text{CS}}$  = High).

After power on, an initial pause of  $150 \,\mu s$  is required prior to the control register access or normal operation. Failure to follow these steps may lead to unpredictable start-up modes.

Please note the default operation mode after power up is the asynchronous SRAM I/F mode (see Chapter 2.4).

Figure 4 Power Up Sequence

Functional Description

## 2.2 Access To The Control Register Map

#### [Disclaimer]

#### Amax for 64Mbit CellularRAM is A21. A22 for 128Mbit density.

Write access to the control register map is enabled by applying the SCR command asserting the CRE-pin to high. In combination with CRE set to high, Pin A19 designates the operation to one of either control registers. Pin A19 set to low selects the Refresh Control Register (RCR), Pin A19 set to high addresses the Bus Configuration Register (BCR), while A18 is applied low.

Write and read access to the control registers is also available at S/W entry method. For details, please refer to "Appendix : S/W Register Entry Mode ("4-cycle method")" on Page 58.

## Figure 5 The two Control Registers (Write and Read access)

A22 is not shown in Figure 5. It has to be set to "0".

Figure 6 Control Register Write (SCR) in Asynchronous command

#### **Functional Description**

**Figure 6** shows SCR command in asynchronous way. CRE is asserted high and the op-code is loaded to the selected register via address bus. A19 selects either BCR (=1) or RCR (=0) while A18 is supplied low.  $\overline{ADV}$  may be held low for entire operation, but  $\overline{CS}$  has to start from high, goes low, then back to high to complete the cycle.

Figure 7 Control Register Read (FCR) in Asynchronous command

FCR command is introduced to this CellularRAM design so that the programmed content of the selected register can be checked. The timing diagram in **Figure 7** is identical to asynchronous read operation except CRE state.

Figure 8 Control Register Write (SCR) in Synchronous Mode

## **Functional Description**

SCR can be performed in synchronous way. CRE sampled high at rising edge of CLK initiates and completes the operation. Please note than WAIT goes deasserted after synchronous SCR command is decoded and  $\overline{CS}$  has to go high to complete the cycle before issuing new command.

Figure 9 Control Register Read (FCR) in Synchronous Mode

FCR in synchronous command is identical to a read burst of single-bit, but high CRE enables read access from the register, not from the memory array. Please note than WAIT goes deasserted after synchronous SCR command is decoded and OE becomes low.

#### Functional Description

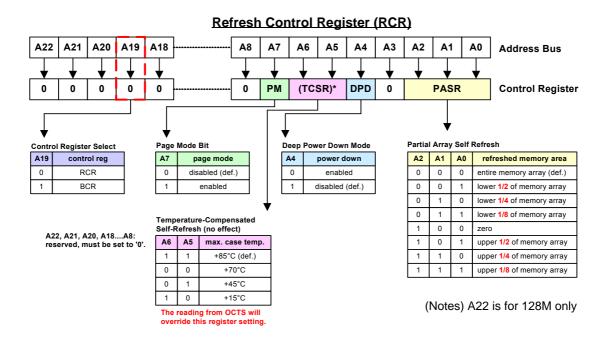

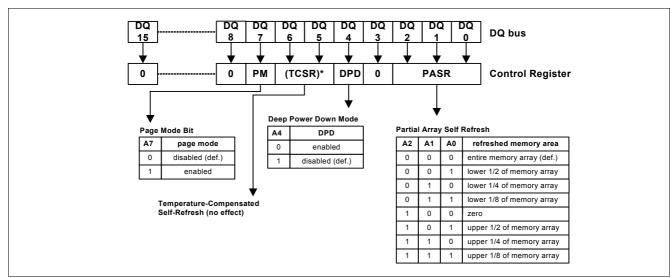

## 2.3 Refresh Control Register

The Refresh Control Register (RCR) allows to save stand-by power additionally by making use of the Partial-Array Self Refresh (PASR) and Deep Power Down (DPD) features. The Refresh Control Register is programmed via the Control Register Set command (with CRE = 1 and A19 = 0) and retains the stored information until it is reprogrammed or the device loses power. The field for the Temperature-Compensated Self Refresh (TCSR) is not in use since OCTS controls and adjusts refresh rate according to die temperature. Any setting of this field has no effect.

Please note that the RCR contents can only be set or changed when the CellularRAM is in idle state.

## RCR Refresh Control Register

## $(CRE, A19 = 10_B)$

| Amax-A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6  | A5  | A4  | A3 | A2 | A1   | A0 |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|-----|-----|-----|----|----|------|----|

| 0        | RS  |     |     |     |     |     | 0   | 1   |     |     |    |    | PM | (тс | SR) | DPD | 0  |    | PASR | 2  |

| Field  | Bits  | Type <sup>1)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|--------|-------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RS     | 19    | -                  | Register Select         0       set to 0 to select this RCR (= 1 to select BCR).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| PM     | 7     | wr                 | Page Mode Enable/DisableIn asynchronous operation mode the user has the option to toggle A0 - A3 in a randomway at higher rate (20 ns vs. 70 ns) to lower access times of subsequent reads with16-word boundary. In synchronous mode this option has no effect. The max. pagelength is 16 words.Please note that as soon as page mode is enabled the $\overline{CS}$ low time restriction applies.This means that the $\overline{CS}$ signal must not be kept low longer than $t_{CSL} = 4 \ \mu s$ . Pleaserefer to Figure 23.00page mode disabled (default)1page mode enabled |  |  |  |  |  |

| (TCSR) | [6:5] | NA                 | <b>Temperature Compensated Self Refresh (Not in use)</b><br>The 2-bit wide TCSR field is not in use. On-chip temperature sensor (OCTS) adjusts<br>the refresh period according to the actual temperature of die. Since DRAM technology<br>requires higher refresh rates at higher temperature this enables the device to lower<br>power consumption in case of low or medium temperatures.<br>All are reserved. Setting has no effect.                                                                                                                                          |  |  |  |  |  |

| DPD    | 4     | wr                 | <ul> <li>Deep Power Down Enable/Disable</li> <li>The DPD control bit puts the CellularRAM device in an extreme low power mode cutting current consumption to less than 25 μA. Stored memory data is not retained in this mode. The settings of both control registers RCR and BCR are maintained during DPD. Please note that the use of DPD mode for duration of no longer than 1ms is strictly prohibited.</li> <li>0 DPD enabled</li> <li>1 DPD disabled (default)</li> </ul>                                                                                                |  |  |  |  |  |

#### Functional Description

| Field | Bits                 | Type <sup>1)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PASR  | [2:0]                | wr                 | Partial Array Self Refresh<br>The 3-bit PASR field is used to specify the active memory array. The active memory<br>array will be kept periodically refreshed whereas the disabled parts will be excluded<br>from refresh and previously stored data will get lost. The normal operation still can be<br>executed in disabled array, but stored data is not guaranteed. This way the customer<br>can dynamically adapt the memory capacity to one's need without paying a power<br>penalty. Please refer to Figure 10.<br>000 entire memory array (default)<br>001 lower 1/2 of the memory array (64 Mb)<br>010 lower 1/4 of the memory array (32 Mb)<br>011 lower 1/8 of the memory array (16 Mb)<br>100 zero<br>101 upper 1/2 of the memory array (32 Mb)<br>110 upper 1/4 of the memory array (32 Mb)<br>111 upper 1/8 of the memory array (32 Mb) |

| Res   | max-20,<br>[18:8], 3 | w                  | Reserved<br>must be set to '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

1) wr: write-read access

## 2.3.1 Partial Array Self Refresh (PASR)

By applying PASR the user can dynamically customize the memory capacity to one's actual needs in normal operation mode and standby mode. With the activation of PASR there is no longer a power penalty paid for the larger CellularRAM memory capacity in case only e.g. 16 Mbits are used by the host system.

Bit2 down to bit0 specify the active memory array and its location (starting from bottom or top memory location). The memory array outside the selected range is powered down immediately after the mode register has been programmed. Advice for the proper register setting including the address ranges is given in Figure 10.

PASR is effective in normal operation and standby mode as soon as it has been configured by register programming. Default setting is the entire memory array.

Figure 11 shows an exemplary PASR configuration where it is assumed that the application uses max. 32 Mbit out of 128 Mbit.

## **Functional Description**

## 2.3.2 Deep Power Down Mode

To put the device in deep power down mode, the DPD control bit must be asserted to low and  $\overline{CS}$  has to be pulled up and maintained high. Once set into this extreme low power mode current consumption is cut down to less than 25 µA until  $\overline{CS}$  goes low automatically resetting the DPD control bit to be disabled.

All internal voltage generators inside the CellularRAM are switched off and the internal self-refresh is stopped. This means that all stored memory information will be lost by entering DPD. Only the register values of BCR and RCR are kept valid during DPD.

A guard time of at least 150  $\mu$ s has to be met where no commands beside a NOP must be applied to re-enter again standby or idle mode.

**Figure 12** helps to overview how DPD mode is entered, maintained, then exited. DPD mode starts from the time when  $\overline{CS}$  is high and the DPD control bits is programmed to low (enabled). Then DPD exit is simply initiated by seeing  $\overline{CS}$  low resulting in automatic reset of the DPD control bit. The time when DPD mode is maintained should exceed **150**µs for proper operation of the CellularRAM.

Figure 12 DPD Entry and Exit

**Table 7** compares several methods available to suppress the power consumption down to deep level. Since wakeup time is required for DPD, it is recommended to use PASR of zero range for relatively short duration in the mode. To chop completely off the residual power consumption, disconneting the power supply from the device must be better.

| Table 7 | Timing Parameters for DPD Operation |

|---------|-------------------------------------|

|---------|-------------------------------------|

| Parameter                 | Symbol            | 9.6, 12. | Unit | Note |   |

|---------------------------|-------------------|----------|------|------|---|

|                           |                   | Min.     | Max. |      |   |

| Duration of DPD operation | t <sub>DPD</sub>  | 150      | _    | μS   | - |

| DPD Exit Time             | t <sub>DPDX</sub> | 10       | _    | μS   | _ |

| DPD Recovery Time         | t <sub>R</sub>    | 150      | _    | μS   | _ |

#### Functional Description

## 2.3.3 Temperature Compensated Self Refresh (TCSR)

The setting of this register has no effect any longer due to the use of OCTS. Actual die temperature is measured and refresh rate is adjusted accordingly by OCTS.

## 2.3.4 Power Saving Potential in Standby When Applying PASR, TCSR or DPD

Table 8

demonstrates the currents in standby mode when PASR, TCSR or DPD is applied. TCSR is for reference only, since it reflects the reading of OCTS instead of external programming of the register.

The values in Table 8 is not tested for all samples in every cases. For reference use only.

| Operation<br>Mode      | Power Mode        | PASR | RCR<br>Control | Wake-Up<br>Phase | Active<br>Array                |                                 | Stand                           | <b>dby [μΑ]</b>                 |                                 |

|------------------------|-------------------|------|----------------|------------------|--------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| NO                     | STANDBY           | TCSR | No (OCTS)      | -                | -                              | 85°                             | 70°                             | 45°                             | 15°                             |

| OPERATION/<br>DESELECT |                   | PASR | Bit2-0         | -                | Full<br>1/2<br>1/4<br>1/8<br>0 | 250<br>170<br>130<br>115<br>100 | 180<br>140<br>120<br>110<br>100 | 140<br>120<br>110<br>105<br>100 | 130<br>120<br>110<br>100<br>100 |

| DPD                    | DEEPPOWER<br>DOWN | DPD  | Bit4           | ~150 µs          | 0                              |                                 | 25.0                            |                                 | 10.0                            |

Table 8

Standby Currents When Applying PASR, TCSR or DPD

## 2.3.5 Page Mode Enable/Disable

In asynchronous operation mode, the user has the option to enable page mode to toggle A0 - A3 in random way at higher cycle rate (20 ns vs. 70 ns) to lower access times of subsequent reads within 16-word boundary. Write operation is not supported in the manner of page mode access. In synchronous mode, this option has no effect. The max. page length is 16 words, so which A0 - A3 is regarded as page-mode address. If the access needs to cross the boundary of 16-word (any difference in A22 - A4), then it should start over new random access cycle by toggling  $\overline{CS}$ .

Please note that as soon as page mode is enabled the  $\overline{CS}$  low time restriction applies. This means that  $\overline{CS}$  signal must not be kept low longer than  $t_{CSL} = 4 \ \mu$ s. Please refer to Figure 23.

#### Functional Description

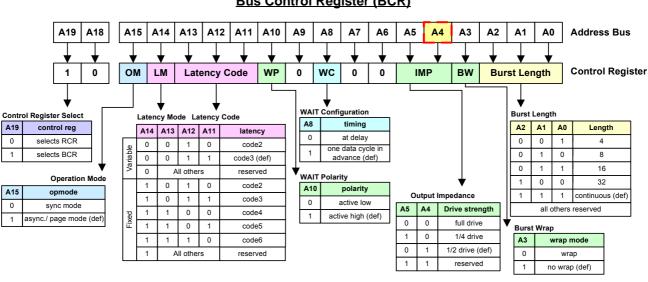

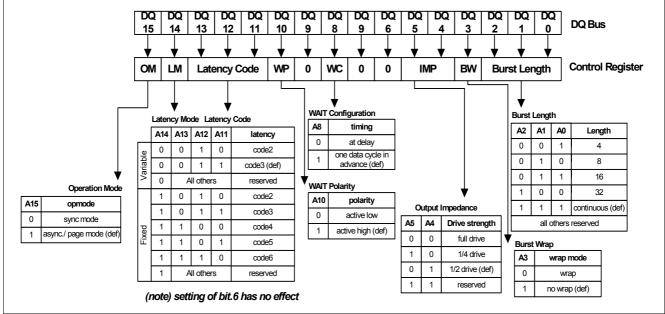

## 2.4 Bus Control Register

The Bus Control Register (BCR) specifies the interface configurations. For the various configuration options please refer to the register description below. The Bus Control Register is programmed via the Control Register Set command (with CRE = 1 and A19 = 1) and retains the stored information until it is reprogrammed or the device loses power. Most of BCR fields are assigned to configure the CellularRAM in a proper way to operate in burst mode and there are some additions to 1st-generation CellularRAM such as fixed latency mode, 32-word burst, etc.

Please note that the BCR contents can only be set or changed when the CellularRAM is in idle state.

Note: Bit 9 and bit 7 must be set to "0" for proper operation and setting of bit 6 has no effect.

| BCR<br>Bus Contr | ol Re | gister  |     |      |       | (CF    | RE, A | 19 = | 11 <sub>B</sub> ) |    |    |    |    |    |    |     |        |      |  |

|------------------|-------|---------|-----|------|-------|--------|-------|------|-------------------|----|----|----|----|----|----|-----|--------|------|--|

| Amax-A20         | A19   | A18-A16 | A15 | A14  | A13   | A12    | A11   | A10  | A9                | A8 | A7 | A6 | A5 | A4 | A3 | A2  | A1     | A0   |  |

| 0                | 1     | 0       | ОМ  | Late | ncy N | lode/0 | Code  | WP   | 0                 | wc | 0  | х  | IN | IP | BW | Bur | st Ler | ngth |  |

| Field               | Bits | Type <sup>1)</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|